Cadence and Google Partner to Scale AI-Driven Chip Design with ChipStack AI Super Agent

TLDR:

- Cadence and Google collaborate to optimize the Cadence ChipStack AI Super Agent with Gemini on Google Cloud

- Platform delivers up to 10X productivity improvements across digital design, testbench development, verification planning, and automated debug

- Uses innovative Mental Model technology for sophisticated agentic reasoning through Cadence native EDA skills

- Available now on Google Cloud Marketplace with click-to-deploy setup

Cadence and Google Cloud: A Strategic Partnership in AI Chip Design

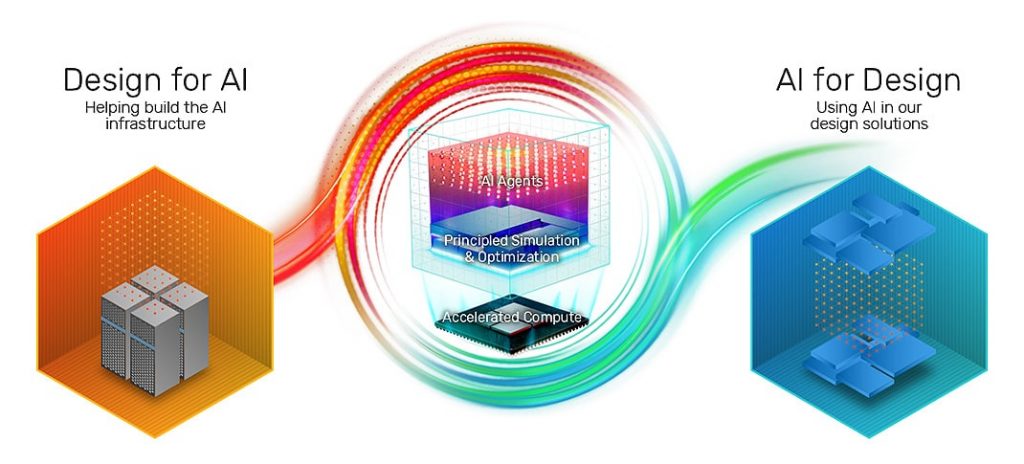

The semiconductor industry is undergoing a fundamental shift — and Cadence just made a big move to lead it. Cadence, a global leader in AI-driven computational software for semiconductor and system design, has announced a strategic collaboration with Google to optimize the Cadence ChipStack AI Super Agent with Gemini on Google Cloud. The goal: bring agentic design automation to the forefront of next-generation chip development.

This isn’t just another partnership announcement. By combining Google’s Gemini large language models with Cadence’s industry-standard EDA (electronic design automation) tools, both companies are building a cloud-native platform that could fundamentally change how chips are designed and verified. Design teams stand to compress development cycles, improve efficiency, and accelerate time to tapeout — all through AI agents that reason, plan, and execute within the EDA workflow.

What the ChipStack AI Super Agent Actually Does

At its core, the ChipStack AI Super Agent integrates advanced agentic reasoning with Cadence’s established EDA solutions. According to Cadence, the platform delivers up to 10X productivity improvements across several critical areas: digital design, testbench development, verification planning, regression management, and automated debug.

The secret sauce is something called Mental Model technology. This enables sophisticated agentic reasoning — essentially, the AI doesn’t just generate code or run simulations; it thinks through complex design problems using Cadence native skills, then drives the EDA tools to improve quality and correctness of the output. By leveraging Google Cloud’s secure, elastic compute infrastructure, the platform also handles the heavy lifting of LLM reasoning, EDA tool execution, and agent orchestration simultaneously.

The result is a “click-to-deploy” end-to-end solution for agent-powered chip design and verification — no extensive on-premise infrastructure required.

Who Benefits Most From This

This collaboration matters most for design teams at foundries, fabless semiconductor companies, system companies, and even aerospace and defense firms working on custom silicon. Any team wrestling with long development cycles, complex verification bottlenecks, or the constant pressure to tape out faster will find value here.

For companies in markets like Malaysia — where the semiconductor ecosystem is growing rapidly — cloud-native AI tools like ChipStack could lower the barrier to advanced chip design. Smaller teams that couldn’t previously afford dedicated EDA infrastructure can now tap into enterprise-grade tools via Google Cloud, paying for what they use rather than investing in permanent on-premise setups.

Paul Cunningham, senior vice president and general manager at Cadence, put it clearly: “By integrating the Cadence ChipStack AI Super Agent with Gemini, we’re advancing the next generation of agentic design — combining the reasoning power of large language models with Cadence’s world-class EDA engines to deliver breakthrough productivity and quality of results.”

Our Take

The Cadence-Google partnership feels significant because both bring something essential to the table. Google has the cloud infrastructure and LLM muscle. Cadence has the EDA domain expertise and toolchain that the semiconductor industry already relies on. Together, they’re bridging the gap between AI reasoning and real-world EDA execution in a way that neither could do alone.

The 10X productivity claim is bold — but in the context of chip design where verification cycles can stretch months, even a 3-4X improvement would be transformative. What makes this particularly interesting is the cloud-native, click-to-deploy approach. It signals a broader industry shift where AI agents don’t just assist human engineers — they actively drive workflows end-to-end.

For the semiconductor industry, this is a glimpse of what’s coming: design environments where AI agents handle the heavy lifting of verification planning, debug, and regression management while engineers focus on architecture and innovation. Whether you’re a large fabless firm or a growing design house, the democratization of AI-driven EDA through the cloud is a trend worth watching closely.

Keyword: Cadence ChipStack AI